Полупроводниковые приборы в России

+7 (812) 240-88-50

+7 (812) 240-88-50

г. Санкт-Петербург, ул. Софийская 17, лит.А, помещение 3Н оф.230

info@texasinst.ru

...

Каталог товаров

Преобразование логики и напряжения

Управление питанием

...

Каталог товаров

Преобразование логики и напряжения

Управление питанием

Поиск

Каталог товаров

Назад

DLP компоненты

Назад

3D scan & machine vision products

Automotive products

Display & projection products

RF & microwave

Назад

Mixers & modulators

RF amplifiers

Wideband transceivers, receivers, transmitters

Аудио

Назад

Audio converters

Audio interface ICs

Specialty audio ICs

Датчики

Назад

Датчики температуры

Магнитные датчики

Радиолокационные датчики миллиметрового диапазона

Драйверы двигателей

Назад

Actuator drivers

Brushless DC (BLDC) motor drivers

Изоляторы

Назад

Isolated interface ICs

Power for signal isolators

Интерфейсы

Назад

Circuit protection ICs

Ethernet ICs

High-speed SerDes

Коммутаторы и мультиплексоры

Микроконтроллеры (MCUs) и процессоры

Преобразование логики и напряжения

Назад

Buffers, drivers & transceiver

Flip-flops, latches & registers

Voltage translators & level shifters

Преобразователи данных

Назад

Аналого-цифровые преобразователи (АЦП)

Интегрированные и специальные функциональные преобразователи данных

Цифроаналоговые преобразователи (ЦАП)

Управление питанием

Назад

AC/DC & isolated DC/DC switching regulators

Battery management ICs

DC/DC switching regulators

Digital power ICs

Gate drivers

MOSFETs

Power over Ethernet (PoE) ICs

Voltage references

Усилители

Назад

Operational amplifiers (op amps)

Назад

Часы и генераторы времени

/ / / / /

ADC12D1620QML-SP Texas instruments

ADC12D1620QML-SP Texas instruments

ADC12D1620QML-SP

Уточнить цену

ADC12D1620QML-SP

Уточнить цену

СРАВНИТЬ

В СРАВНЕНИИ

Уточнить цену

Описание

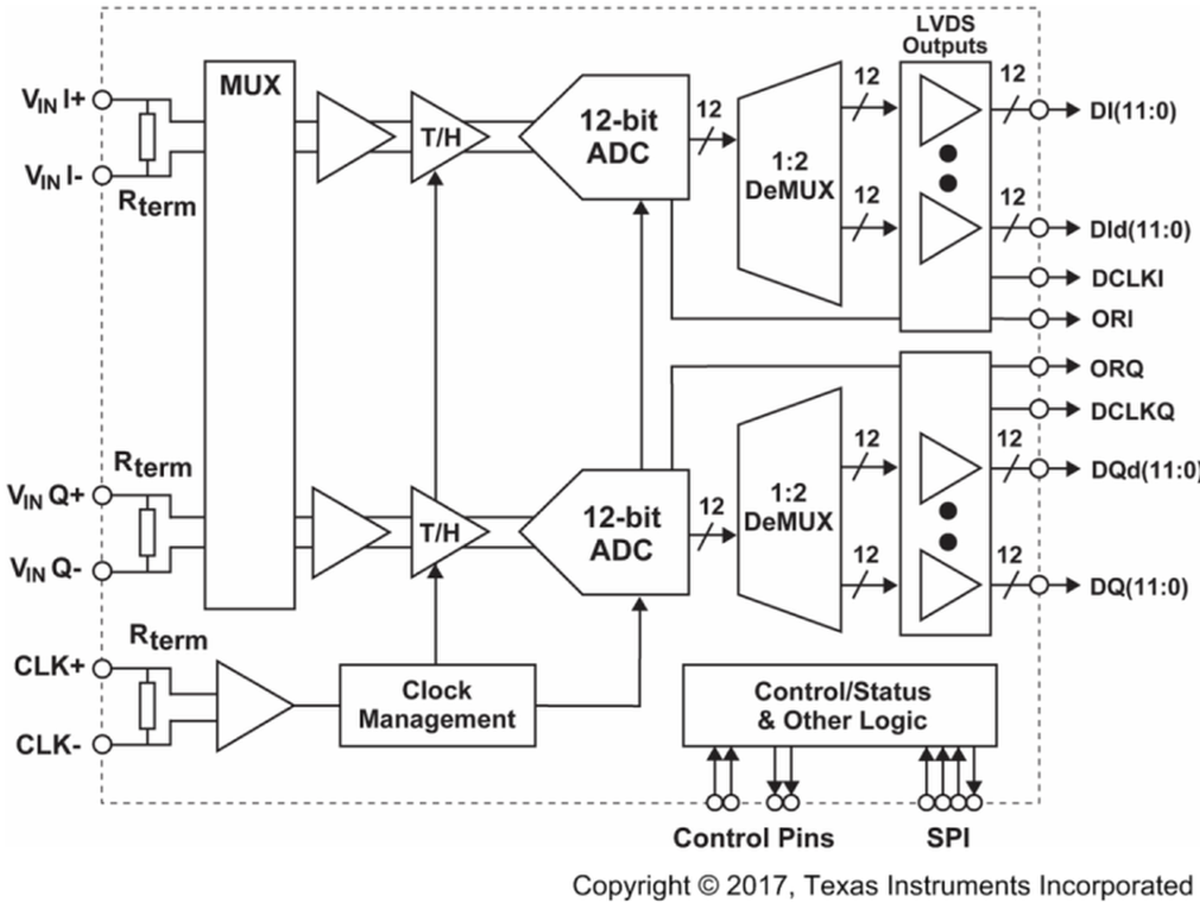

The ADC12D1620QML uses a package redesign to achieve better ENOB, SNR, and X-talk compared to the ADC12D1600QML. As is its predecessor, the ADC12D1620QML is a low-power, high-performance CMOS analog-to-digital converter (ADC) that digitizes signals at a 12-bit resolution at sampling rates up to 3.2 GSPS in an interleaved mode. It can also be used as a dual-channel ADC for sampling rates up to 1.6 GSPS. For sampling rates below 800 MHz, there is a low-sampling power-saving mode (LSPSM) that reduces power consumption to less than 1.4 W per channel (typical). The ADC can support conversion rates as low as 200 MSPS.

- Total ionizing dose (TID) to 300 krad(Si)

- Single event functional interrupt (SEFI) tested

- Single event latch-up (SEL) > 120 MeV-cm2/mg

- Cold sparing capable

- Wide temperature range –55°C to +125°C

- Power consumption = 3.8 W or 2.7 W (1600- or 800-MHz clock)

- 3-dB Input bandwidth = 3 GHz

- Low-sampling power-saving mode (LSPSM) reduces power consumption and improves performance for fCLK ≤ 800 MHz

- Auto-sync function for multi-chip systems

- Time stamp feature to capture external trigger

- Test patterns at output for system debug

- 1:1 Non-demuxed or 1:2 or 1:4 parallel demuxed LVDS outputs

- Single 1.9-V power supply

| Sample rate (max) (Msps) | 1600, 3200 |

| Resolution (Bits) | 12 |

| Number of input channels | 1, 2 |

| Interface type | Parallel LVDS |

| Analog input BW (MHz) | 2400 |

| Features | Ultra High Speed |

| Rating | Space |

| Peak-to-peak input voltage range (V) | 0.8 |

| Power consumption (typ) (mW) | 3880 |

| Architecture | Folding Interpolating |

| SNR (dB) | 59.8 |

| ENOB (Bits) | 9.5 |

| SFDR (dB) | 67.4 |

| Operating temperature range (°C) | -55 to 125, 25 to 25 |

| Input buffer | Yes |

| Radiation, TID (typ) (krad) | 300 |

| Radiation, SEL (MeV·cm2/mg) | 120 |

г. Санкт-Петербург, ул. Софийская 17, лит.А, помещение 3Н оф.230